KHÓA MẬT MÃ DÙNG VI ĐIỀU KHIỂN

NỘI DUNG ĐỒ ÁN

Đề Tài : KHÓA MẬT MÃ DÙNG VI ĐIỀU KHIỂN

LỜI NÓI ĐẦU

Ngày nay, với những ứng dụng của khoa học kỹ thuật tiên tiến, thế giới của chúng ta đã và đang một ngày thay đổi, văn minh và hiện đại hơn. Sự phát triển của kỹ thuật điện tử đã tạo ra hàng lọat những thiết bị với các đặc điểm nổi bật như sự chính xác cao, tốc độ nhanh, gọn nhẹ là những yếu tố rất cần thiết góp phần cho họat động của con người đạt hiệu quả cao.

Điện tử đang trở thành một ngành khoa học đa nhiệm vụ. Điện tử đã đáp ứng được những đòi hỏi không ngừng từ các lĩnh vực công–nông-lâm-ngư nghiệp cho đến các nhu cầu cần thiết trong họat động đời sống hằng ngày.

Một khi đã học về ngành Điện tử, bản thân người học mong muốn sẽ có cơ hội sử dụng những kiến thức đã học để tạo ra một sản phẩm có ích cho xã hội cũng như chính bản thân và đó cũng là dịp để đánh giá lại kiến thức có được trong suốt quá trình học tập và rèn luyện tại trường.

Được sự hướng đẫn và giúp đỡ tận tình của thầy , em đã thực hiện đề tài “Khóa mật mã dùng vi điều khiển“.

Đề tài lấy môn Vi Xử Lý làm trọng tâm. Lấy ý tưởng cái khóa để thực hiện đề tài. So sánh hai đọan mã để đưa ra kết luận đúng hoặc sai, nếu đúng thì thực hiện nếu sai thì cảnh báo cho người sử dụng.

Đề tài được hoàn tất nhờ vào sự nổ lực của bản thân cùng sự nhiệt tình chỉ bảo của các thầy, các cô trong khoa.

Tuy đã cố gắng nhưng trong quá trình thực hiện không tránh khỏi sai sót. Kính mong được sự chỉ bảo của các thầy, cô và ý kiến đóng góp của bạn bè.

Cuối cùng em xin cảm ơn nhà trường đã cho em một môi trường học tập tốt và lành mạnh, xin cảm ơn các thầy các cô về những kiến thức đã được học.

thực hiện: Lại Tấn Thịnh

MỤC LỤC

Chương I : Giới thiệu các linh kiện sử dụng

A . IC AT89C51 4

B . IC 555 11

Chương II : Thiết kế mạch

1. Khối OSC 14

2. Khối RESET 15

3. Khối giao tiếp bàn phím 15

4. Khối báo động 15

5. Khối đảo chiều động cơ 16

Sơ đồ nguyên lý 17

Chương III : Thiết kế chương trình

I . Chương trình giao tiếp bàn phím 18

II . Chương trình chính 22

Chương kết luận

CHƯƠNG I : GIỚI THIỆU CÁC LINH KIỆN SỬ DỤNG

A . IC AT89C51:

I . Tổng quan về phần cứng:

1. Mô tả :

AT89C51 là một hệ vi tính 8-bit đơn chip CMOS có hiệu suất cao, công suất nguồn tiêu thụ thấp và có 4K byte bộ nhớ ROM Flash xoá được / lập trình được . Chip này được sản xuất dưạ vào công nghệ bộ nhớ không mất nội dung có độ tích hợp cao của Atmel.

AT89C51 có các đặc trưng chuẩn sau :

-4K byte Flash.

-128 byte RAM.

-32 đường xuất nhập.

- Hai bộ định thơì / đếm 16-bit.

- Một cấu trúc ngắt hai mức ưu tiên và 5 nguyên nhân ngắt.

-Một port nối tiếp song công.

-Mạch dao động và tạo xung clock trên chip.

2 . Mô tả các chân :

VCC Chân cung cấp điện

GND Chân nối đất ( 0V )

Port 0 :

Là port xuất nhập 8-bit hai chiều cực D hở. Khi làm nhiệm vụ là port xuất, mỗi chân của port có thể hút dòng của 8 ngõ vaò TTL . Khi các logic 1 được ghi vào các chân của port 0, các chân có thể được sử dụng làm các ngỏ vào tổng trở cao.

Port 1 :

Là port xuất nhập 8-bit hai chiều có các điện trở kéo lên bên trong . Các bộ đệm xuất của port có thể hút và cấp dòng với 4 ngõ vào TTL . Khi các logic 1 được ghi vào các chân của port 1 , các chân này được kéo lên mức cao bởi các điện trở kéo lên bên trong và có thể được sử dụng như là các ngõ vào.

Port 2 :

Là port xuất nhập 8-bit hai chiều có các điện trở kéo lên bên trong . Các bộ đệm xuất của port có thể hút và cấp dòng với 4 ngõ vào TTL . Khi các logic 1 được ghi vào các chân của port 2 , các chân này được kéo lên mức cao bởi các điện trở kéo lên bên trong và có thể được sử dụng như là các ngõ vào . Khi làm nhiệm vụ port nhập , các chân của port 2 đang được kéo xuống mức thấp do tác động bên ngoài sẽ cấp dòng do các điện trở kéo lên bên trong .

Port 3 :

Là port xuất nhập 8-bit hai chiều có các điện trở kéo lên bên trong . Các bộ đệm xuất của port có thể hút và cấp dòng với 4 ngõ vào TTL . Khi các logic 1 được ghi vào các chân của port 3 , các chân này được kéo lên mức cao bởi các điện trở kéo lên bên trong và có thể được sử dụng như là các ngõ vào . Khi làm nhiệm vụ port nhập , các chân của port 3 đang được kéo xuống mức thấp do tác động bên ngoài sẽ cấp dòng do các điện trở kéo lên bên trong.

Mỗi chân của port có các chức năng riêng :

|

Bit |

Tên |

Chức năng chuyển đổi |

|

P3.0 P3.1 P3.2 P3.3 P3.4 P3.5 P3.6 P3.7 |

RXT TXD INT0 INT1 T0 T1 WR RD |

Ngõ vào dữ liệu nối tiếp. Ngõ xuất dữ liệu nối tiếp. Ngõ vào ngắt cứng thứ 0. Ngõ vào ngắt cứng thư 1. Ngõ vào củaTIMER/COUNTER thứ 0. Ngõ vào củaTIMER/COUNTER thứ 1. Tín hiệu ghi dữ liệu lên bộ nhớ ngoài. Tín hiệu đọc bộ nhớ dữ liệu ngoài.

|

RST :

Ngõ vào Reset. Mức cao trên chân này trong 2 chu kỳ máy trong khi bộ dao động đang hoạt động sẽ reset AT89C51

ALE / : xung của ngõ ra cho phép chốt địa chỉ ALE cho phép chốt byte thấp của địa chỉ trong thời gian truy xuất bộ nhớ ngoài .

: chân cho phép bộ nhớ chương trình điều khiển truy xuất bộ nhớ chương trình ngoài

/ VPP nên nối với VCC để thực thi chương trình bên trong chip

II . Tóm lược tập lệnh :

1 . Giới thiệu :

Vi điều khiển 8951 có mã lệnh 8 bit cung cấp tất cả 28=256 lệnh, nhưng thực tế chỉ dùng 255 lệnh ,trong đó có 139 lệnh 1 byte, 92 lệnh 2 byte và 24 lệnh 3 byte.

2 . Các chế độ định địa chỉ :

8951 có 8 mode định địa chỉ như sau:

-Thanh ghi

- Trực tiếp

- Gián tiếp

- Tức thì

- Quan hệ

- Tuyệt đối

- Dài (Long)

- Index

3 . Định địa chỉ thanh ghi ( Register ) :

8951 có 4 nhóm thanh ghi làm việc (Bank 0 – Bank 3), mỗi nhóm có 8 thanh ghi R0 – R7. 4 nhóm thanh ghi này chiếm 32 byte đầu tiên trong chip RAM (địa chỉ 00H – 1 FH). Để chọn nhóm thanh ghi làm việc ta dùng bit 4 và bit 3 của Từ trạng thái chương trình PSW (mặc định dùng Bank 0), mỗi lần chỉ có 1 Bank làm việc.

Ví dụ: MOV PSW , # 00011000B ; chọn Bank 3

ADD A , R7

Một số lệnh chỉ định 1 thanh ghi nào đó chẳng hạn như bộ tích lũy ACC, data pointer DPTR … do đó các bit địa chỉ là không cần thiết, ví dụ : INC DPTR.

4 . Định địa chỉ trực tiếp (Direct) :

Định địa chỉ trực tiếp có thể truy xuất bất kỳ biến và thanh ghi nào

Ví dụ: MOV P1,A

5. Định địa chỉ gián tiếp (Indirect) :

Dùng R0 và R1 như là thanh ghi “pointer” mà nội dung của nó trỏ đến 1 địa chỉ nào đó trong RAM nơi mà dữ liệu được ghi hoặc đọc. Định địa chỉ gián tiếp được biểu diễn bởi dấu @ trước R0 và R1. Ví dụ: xóa RAM nội từ địa chỉ 60H đến 7FH:

MOV R0,#60H

LOOP: MOV @R0,#0

INC R0

CJNE R0,#80H,LOOP

(continue)

6 . Định địa chỉ tức thì (Immediate) :

Toán hạng tức thì được dẫn đầu bởi dấu # . Toán hạng tức thì có thể là 1 hằng số, 1 biến kí tự hoặc 1 biểu thức số học.

Ví dụ: MOV A,#12

MOV DPTR,#8000H

7 . Định địa chỉ quan hệ(Relative) :

Chỉ dùng cho lệnh nhảy. Một địa chỉ quan hệ (offset) là 1 giá trị có dấu 8 bit được cộng vào PC thành địa chỉ của lệnh thực thi kế tiếp. Phạm vi nhảy là –128 đến +127

Ví dụ: nếu nhãn THERE biểu diển 1 lệnh tại vùng nhớ 1040H và lệnh SJMP THERE ở vùng nhớ 1000H và 1001H . Khi dịch sẽ gán 1 offset quan hệ là 3EH (1002H+3EH=1040H).

8 . Định địa chỉ tuyệt đối (Absolute):

Chỉ dùng cho lệnh ACALL và AJMP. Hai lệnh này cho phép rẽ nhánh trong trang 2K hiện hành của bộ nhớ mã lệnh bằng cách chia 11 bit LSB của địa chỉ đích trong opcode (A10-A8) và byte 2 của lệnh (A7-A0).

5 bit cao của địa chỉ đích là 5 bit cao hiện hành trong bộ đếm chương trình, vì thế lệnh sau lệnh rẽ nhánh và đích đến của lệnh rẽ nhánh phải nằm trong cùng trang 2K vì A15-A11 không đổi.

9 . Định địa chỉ dài (Long) :

Chỉ dùng cho lệnh LCALL và LJMP. Lệnh 3 byte này có đầy đủ 16 bit địa chỉ đến. Tiện ích của điều này là có thể sử dụng hết vùng code 64K, nhưng bất lợi ở chổ là lệnh dài 3 byte và phụ thuộc vị trí. Sự phụ thuộc vị trí là bất lợi bởi vì chương trình không thể thực thi tại các địa chỉ khác

10 . Định địa chỉ Index :

Sử dụng 1 thanh ghi nền (bộ đếm chương trình PC hay con trỏ dữ liệu DPTR) và 1 offset (bộ tích lũy A). Ta có thể dễ dàng tạo ra bảng nhảy hay bảng look-up bằng cách dùng chế độ định địa chỉ này.

Bản đồ bộ nhớ Data trên Chip như sau:

|

7F |

|

FF |

|

|

|||||||||||||||

|

|

|

|

F0 |

F7 |

F6 |

F5 |

F4 |

F3 |

F2 |

F1 |

F0 |

B |

|||||||

|

|

RAM đa dụng |

|

|

|

|

||||||||||||||

|

|

|

|

E0 |

E7 |

E6 |

E5 |

E4 |

E3 |

E2 |

E1 |

E0 |

ACC |

|||||||

|

|

|

|

|

|

|

||||||||||||||

|

|

|

|

D0 |

D7 |

D6 |

D5 |

D4 |

D3 |

D2 |

D1 |

D0 |

PSW |

|||||||

|

|

|

|

|

|

|

||||||||||||||

|

30 |

|

|

B8 |

- |

- |

- |

BC |

BB |

BA |

B9 |

B8 |

IP |

|||||||

|

2F |

7F |

7E |

7D |

7C |

7B |

7A |

79 |

78 |

|

|

|

|

|

|

|

|

|

|

|

|

2E |

77 |

76 |

75 |

74 |

73 |

72 |

71 |

70 |

|

B0 |

B7 |

B6 |

B5 |

B4 |

B3 |

B2 |

B1 |

B0 |

P.3 |

|

2D |

6F |

6E |

6D |

6C |

6B |

6A |

69 |

68 |

|

|

|

|

|

|

|

|

|

|

|

|

2C |

67 |

66 |

65 |

64 |

63 |

62 |

61 |

60 |

|

A8 |

AF |

|

|

AC |

AB |

AA |

A9 |

A8 |

IE |

|

2B |

5F |

5E |

5D |

5C |

5B |

5A |

59 |

58 |

|

|

|

|

|

|

|

|

|

|

|

|

2A |

57 |

56 |

55 |

54 |

53 |

52 |

51 |

50 |

|

A0 |

A7 |

A6 |

A5 |

A4 |

A3 |

A2 |

A1 |

A0 |

P2 |

|

29 |

4F |

4E |

4D |

4C |

4B |

4A |

49 |

48 |

|

|

|

|

|

|

|

|

|

|

|

|

28 |

47 |

46 |

45 |

44 |

43 |

42 |

41 |

40 |

|

99 |

không được địa chỉ hoá bit |

SBUF |

|||||||

|

27 |

3F |

3E |

3D |

3C |

3B |

3A |

39 |

38 |

|

98 |

9F |

9E |

9D |

9C |

9B |

9A |

99 |

98 |

SCON |

|

26 |

37 |

36 |

35 |

34 |

33 |

32 |

31 |

30 |

|

|

|

|

|||||||

|

25 |

2F |

2E |

2D |

2C |

2B |

2A |

29 |

28 |

|

90 |

97 |

96 |

95 |

94 |

93 |

92 |

91 |

90 |

P1 |

|

24 |

27 |

26 |

25 |

24 |

23 |

22 |

21 |

20 |

|

|

|

|

|||||||

|

23 |

1F |

1E |

1D |

1C |

1B |

1A |

19 |

18 |

|

8D |

không được địa chỉ hoá bit |

TH1 |

|||||||

|

22 |

17 |

16 |

15 |

14 |

13 |

12 |

11 |

10 |

|

8C |

không được địa chỉ hoá bit |

TH0 |

|||||||

|

21 |

0F |

0E |

0D |

0C |

0B |

0A |

09 |

08 |

|

8B |

không được địa chỉ hoá bit |

TL1 |

|||||||

|

20 |

07 |

06 |

05 |

04 |

03 |

02 |

01 |

00 |

|

8A |

không được địa chỉ hoá bit |

TL0 |

|||||||

|

1F |

Bank 3 |

|

89 |

không được địa chỉ hoá bit |

TMOD |

||||||||||||||

|

18 |

|

|

88 |

8F |

8E |

8D |

8C |

8B |

8A |

89 |

88 |

TCON |

|||||||

|

17 |

Bank 2 |

|

87 |

không được địa chỉ hoá bit |

PCON |

||||||||||||||

|

10 |

|

|

|

|

|

||||||||||||||

|

0F |

Bank 1 |

|

83 |

không được địa chỉ hoá bit |

DPH |

||||||||||||||

|

08 |

|

|

82 |

không được địa chỉ hoá bit |

DPL |

||||||||||||||

|

07 |

Bank thanh ghi 0 |

|

81 |

không được địa chỉ hoá bit |

SP |

||||||||||||||

|

00 |

(mặc định cho R0 -R7) |

|

88 |

87 |

86 |

85 |

84 |

83 |

82 |

81 |

80 |

P0 |

|||||||

B . IC 555 :

Sơ đồ chức năng

Công dụng của các chân:

Chân số 1 (GND)

Cho nối masse để lấy dòng cấp cho IC ,dòng điện tử sẽ từ masse chảy vào IC.

Chân số 2 (TRIGGER)

Ngã vào của một tầng so áp 2. Ở đây mức áp chuân bằng 1/3VCC ,lấy trên cầu chia Volt tạo bởi 3 điện trở 5K.Khi mức áp trên chân 2 xuống đến mức 1/3VCC thì trên chân 3 sẽ chuyển lên mức áp cao, lúc này khoá điện trên chân số 7 sẽ ở trạng thái hở.

Chân số 3 (OUTPUT)

Ngã ra,tín hiệu ở ngã ra có dạng xung (mức áp không thấp thì cao).Khi chân 2 xuống thấp hơn mức áp chuẩn 1/3VCC thì chân 3 lên mức áp cao và khi chân 6 lên cao hơn mức áp chuẩn 2/3VCC thì chân 3 xuống mức áp thấp.

Chân số 4 (RESET)

Chân hồi nguyên, chân Reset xác lập trạng thái ngõ ra.Khi chân số 4 cho nối masse (đặt ở mức áp thấp) thì chân 3 sẽ bị chốt ở mức áp thấp,chỉ khi chân 4 đặt ở mức áp cao thì ngã ra mới được tự do,và mới có thể lúc lên cao lúc xuống thấp.

Chân số 5 (CONTROL VOLTAGE)

Chân điều khiển, qua chân này làm thay đổi các mức áp chuẩn trên cầu chia Volt .Khi mức áp chuẩn cấp cho các tầng so áp 1 và 2 bị thay đổi thì tần số tín hiệu cũng thay đổi theo.Người ta thường đưa điện áp tín hiệu vào chân 5 để thực hiện sự điều chế tần số.

Chân số 6 (THRESHOLD)

Ngã vào của một tầng so áp một .Có mức áp chuẩn bằng 2/3 VCC ,lấy trên cầu chia Volt tạo bởi 3 điện trở 5K .Khi mức áp trên chân 6 lên đến mức 2/3 VCC thì chân 3 sẽ chuyển xuống mức áp thấp,lúc này khoá điện trên chân số 7 sẽ ở trạng thái đóng kín

Chân số 7 (DISCHARGE)

Chân xả điện, chân này là ngã ra của một khoá điện đóng mở theo áp,khoá điện này đóng mở theo điện áp trên chân số 3.Khi chân số 3 ở mức áp cao thì khoá điện đóng lại và sẽ cho dòng chảy ra và khi chân 3 ở mức áp thấp thì khoá điện hở ,cắt dòng.

Chân số 8 (VCC)

Chân nguồn, nối vào nguồn nuôi Vcc để cấp điện cho IC 555 với mức nguồn nuôi từ 3V đến 18V.

Các tham số giới hạn của IC 555 với mạch điện ráp bằng loại transistor Bipolar

- Nguồn nuôi +18V

- Dòng điện ngã ra 200mA

- Công suất tiêu tán trên IC 600mW

Các tham số giới hạn của IC 555 với mạch điện ráp bằng loại transistor C- MOS

- Nguồn nuôi +18V

- Dòng điện ngã ra 100mA

- Công suất tiêu tán trên IC 200mW

Thời gian xung ra ở mức áp cao là:

T1 » 0,693(R1+R2)C1 sec

(Trong đó R1 ,R2 tính theo MW, C1 tính theo mF)

Thời gian xung ra ở mức áp thấp là:

T2 » 0,693R2C1 sec

Chu kỳ của tín hiệu: T=T1 +T2

Tần số của tín hiệu: f=1/(T1+T2)=1/0,693(R1+2R2)C1 Hz

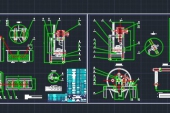

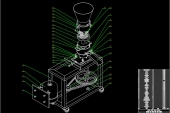

CHƯƠNG II : THIẾT KẾ MẠCH

Sơ đồ khối :

1 . Khối OSC :

Khối tạo dao động cho toàn mạch sử dụng thạch anh 12Mhz tạo ra 1 chu kỳ máy là 1 ms .

Khối được thiết kế như sau :

2 . Khối Reset :

Khởi động lại mạch bằng cách nhấn nút SW2 , lúc này dữ liệu bị xóa sạch

3 . Khối giao tiếp bàn phím :

Dùng để nhập mã số

4 . Khối báo động :

Cảnh báo khi nhập mã sai quá 3 lần . Ở đây , IC 555 làm nhiệm vụ tạo xung nhịp

Bình thường P3.4 ở mức áp cao nên IC 555 không thể hoạt động . Khi mã số cửa được nhập sai quá 3 lần thì P3.4 được chuyển xuống mức áp thấp 0V làm cho transistor được phân cực , IC 555 hoạt động . Chỉ khi nào nhập đúng mã thì P 3.4 mới chuyển lên mức áp cao thì cói mơí dừng báo động . Biến trở 100k dùng để điều chỉnh nhịp kêu của còi .

Thiết kế mạch :

Điều kiện để 1 transistor dẫn bão hòa :

- IB > IC /

- VBE ≥ 0,8V

Điều kiện để 1 transistor dẫn bão hòa : VBE ≥ 0,8V

Ta có :

IC = IL= ( VCC - VCE ) / RRELAY

= (12 – 0,2 ) / 400

= 29,5mA

IBSAT = IC / min = 29,5 / 200 = 0,1475 mA

Với K = 2 ÷ 5 :hệ số an tòan

Chọn IB = 2. IBSAT = 0,295 mA

5V = IB.R3 + VBE

→ R3 = ( 5V – VBE ) / IB

= 14,2K . Chọn R3 = 15K

5.Khối đảo chiều động cơ :

Hoạt động :

Khi P3.0 lên mức cao 5V , P3.1 xuống mức thấp → Q1 dẫn , Q2 đóng→ Role đóng→ Motor hoạt động

Ngược lại , khi P3.0 xuống mức thấp , P3.1 lên mức cao 5V → Q1 đóng , Q2 dẫn → Role đóng→ Motor hoạt động

II. Sơ đồ nguyên lý

CHƯƠNG III : THIẾT KẾ CHƯƠNG TRÌNH

I. Chương trình giao tiếp bàn phím :

1. Lưu đồ giải thuật :

Chương trình con IN –HEX : chương trình con có nhiệm vụ chống rung phím bằng cách lập lại GET –KEY khoảng 50 lần. Nếu như 50 lần đều trả về C =1 tức là có một phím bị nhấn, còn nếu có một lần C =0 thì đó là rung động và bộ đếm được Reset. Sau khi đã phát hiện có một phím được ấn, IN –HEX sẽ chờ một khoảng thời gian tương ứng với 50 lần gọi GET –KEY để đảm bảo rằng không còn rung cho lần gọi GET –KEY kế tiếp.

2.Chương trình :

***********************************************************

IN_HEX: nhập mã số hex từ bàn phím có chống nảy khi ấn và nhả phím

( 50 lần cho ấn phím và 50 lần cho nhả phím )

***********************************************************

IN_HEX: MOV R3,#50 ; số đếm

BACK: CALL GET_KEY ; phím được ấn ?

JNC IN_HEX ; không : kiểm tra lại

DJNZ R3,BACK ; có : lặp lại 50 lần

PUSH ACC ; lưu mã số hex

BACK2: MOV R3,#50 ; chờ phím nhả

BACK3: CALL GET_KEY ; phím được ấn ?

JC BACK2 ; có : kiểm tra lại

DJNZ R3,BACK3 ; không : lặp lại 50 lần

POP ACC ; khôi phục số hex và

RET ; quay về

***********************************************************

GET_KEY: _ đọc trạng thái bàn phím

_ trả về C = 0 nếu không có phím ấn

_ trả về C = 1 và mã số hex trong ACC nếu có phím ấn

***********************************************************

GET_KEY: MOV A,#0FEH ; bắt đầu với cột 0

MOV R6,#4 ; sử dụng R6 làm bộ đếm

TEST: MOV P1,A ; tích cực cột

MOV R7,A ; lưu ACC

MOV A,P1 ; đọc trở lại port 1

ANL A,#0F0H ; cách ly các hàng

CJNE A,#0F0H,KEY_HIT ; hàng tích cực ?

MOV A,R7 ; không : di chuyển tới

RL A ; cột kế

DJNZ R6,TEST ;

CLR C ; không có phím được ấn

SJMP EXIT ; quay về với C = 0

KEY_HIT: MOV R7,A ; lưu trong R7

MOV A,#4 ; chuẩn bị tính

CLR C ; trọng số của cột

SUBB A,R6 ; 4 – R6 = trọng số

MOV R6,A ; lưu trong R6

MOV A,R7 ; phục hồi mã quét

SWAP A ; đặt trong 4 bit thấp

MOV R5,#4 ; dùng R5 làm bộ đếm

AGAIN: RRC A ; quay cho đến khi = 0

JNC DONE ; thực thi xong khi C= 0

INC R6 ; cộng 4 cho đến khi

INC R6 ; tìm thấy hàng tích cực

INC R6

INC R6

DJNZ R5,AGAIN

DONE: SETB C ; C = 1( có phím được ấn)

MOV A,R6 ; mã trong A

EXIT: RET

II. Chương trình chính .

1 . Lưu đồ giải thuật .

2 . Chương trình .

MCS-51 MACRO ASSEMBLER TAM 10/08/:5 PAGE 1

DOS 7.10 (038-N) MCS-51 MACRO ASSEMBLER, V2.2

OBJECT MODULE PLACED IN C:\LOI\DA\DA1.OBJ

ASSEMBLER INVOKED BY: ??? C:\LOI\DA\DA1.asm

LOC OBJ LINE SOURCE

1

0000 2 ORG 0000H

0000 020003 3 LJMP MAIN

0003 758901 4 MAIN: MOV TMOD,#01H

0006 7580FF 5 MOV P0,#0FFH

0009 7560FE 6 MOV 60H,#11111110B

000C 7561FC 7 MOV 61H,#11111100B

000F 7562F8 8 MOV 62H,#11111000B

0012 7563F0 9 MOV 63H,#11110000B

0015 7564E0 10 MOV 64H,#11100000B

0018 7565C0 11 MOV 65H,#11000000B

001B 756680 12 MOV 66H,#10000000B

001E 756700 13 MOV 67H,#00000000B

14 ;MOV P3,#01110000B ;DEN XANH(CUA MO)17

0021 C2B4 15 CLR P3.4

0023 D2B5 16 SETB P3.5

0025 D2B6 17 SETB P3.6

0027 C2B7 18 CLR P3.7

0029 C2B0 19 CLR P3.0

002B C2B1 20 CLR P3.1

002D 7860 21 MOV R0,#60H ;0:SANG 1:TAT

002F 7930 22 MOV R1,#30H ;CHO NHAP SO LAN 1

0031 120306 23 IN_HEX: LCALL NHAPMA

24 ;MOV P3,#01010000B

0034 C2B4 25 CLR P3.4

0036 D2B6 26 SETB P3.6

0038 C2B7 27 CLR P3.7

003A C2B0 28 CLR P3.0

003C C2B1 29 CLR P3.1

003E C2B5 30 CLR P3.5

0040 1202CA 31 CALL DELAY1

32 ;MOV P3,#01110000B

0043 D2B5 33 SETB P3.5

0045 B40136 34 CJNE A,#01H,MN

0048 AB23 35 MOV R3,23H

004A BBFF05 36 CJNE R3,#0FFH,HAILAN

004D 752300 37 MOV 23H,#0H

0050 8005 38 SJMP XOA

0052 85FF23 39 HAILAN: MOV 23H,0FFH

0055 80DA 40 JMP IN_HEX

0057 757F00 41 XOA: MOV 7FH,#0H

005A 7830 42 MOV R0,#30H ;XOA RAM DE NHAP MA MOI

005C 7600 43 LOOP11: MOV @R0,#0

005E 08 44 INC R0

005F B838FA 45 CJNE R0,#38H,LOOP11

46 ;MOV P3,#01010000B

0062 C2B4 47 CLR P3.4

0064 D2B6 48 SETB P3.6

0066 C2B7 49 CLR P3.7

MCS-51 MACRO ASSEMBLER TAM 10/08/:5 PAGE 2

LOC OBJ LINE SOURCE

0068 C2B0 50 CLR P3.0

006A C2B1 51 CLR P3.1

006C C2B5 52 CLR P3.5

006E 1202F2 53 LCALL DELAY4

54 ;MOV P3,#01110000B

0071 D2B5 55 SETB P3.5

0073 7860 56 MOV R0,#60H

0075 7930 57 MOV R1,#30H

0077 80B8 58 JMP IN_HEX

0079 B4011F 59 PHIM1: CJNE A,#01H,MN2 ;PHIM XOA MA

007C 80B3 60 JMP IN_HEX

007E 752300 61 MN: MOV 23H,#0H

0081 B4034D 62 CJNE A,#03H,IN

63 ;MOV P3,#10110010B ;DEN DO(CUA DONG)16

0084 D2B7 64 SETB P3.7

0086 D2B5 65 SETB P3.5

0088 C2B4 66 CLR P3.4

008A D2B1 67 SETB P3.1

008C C2B6 68 CLR P3.6

008E C2B0 69 CLR P3.0

0090 1202B6 70 CALL DELAY2

71 ;MOV P3,#10110000B

0093 C2B1 72 CLR P3.1

0095 757F00 73 MOV 7FH,#0H

0098 0200FC 74 JMP L5

009B AB39 75 MN2: MOV R3,39H

009D BBFE05 76 CJNE R3,#0FEH,N1

00A0 B40230 77 CJNE A,#02H,X2

00A3 800B 78 SJMP N4

00A5 AB39 79 N1: MOV R3,39H

00A7 BBFF1F 80 CJNE R3,#0FFH,N2

00AA 753900 81 MOV 39H, #00H

00AD B40214 82 CJNE A,#02H,X3

00B0 7580FF 83 N4: MOV P0,#0FFH

00B3 7830 84 MOV R0,#30H ;XOA RAM DE NHAP MA MOI

00B5 7600 85 LOOP5: MOV @R0,#0

00B7 08 86 INC R0

00B8 B838FA 87 CJNE R0,#38H,LOOP5

00BB 7860 88 MOV R0,#60H

00BD 7930 89 MOV R1,#30H

00BF 753900 90 MOV 39H,#00H

00C2 0131 91 JMP IN_HEX

00C4 B40325 92 X3: CJNE A,#03H,N5

00C7 800D 93 SJMP N3

00C9 B40202 94 N2: CJNE A,#02H,X1 ;PHIM XOA

00CC 0131 95 JMP IN_HEX

00CE B4031B 96 X1: CJNE A,#03H,N5 ;PHIM ENTER

00D1 0131 97 IN: JMP IN_HEX

00D3 B403FB 98 X2: CJNE A,#03H,IN

99 ;MOV P3,#10110010B ;DEN DO(CUA DONG)16

00D6 D2B7 100 N3: SETB P3.7

00D8 D2B5 101 SETB P3.5

00DA C2B4 102 CLR P3.4

00DC D2B1 103 SETB P3.1

00DE C2B6 104 CLR P3.6