ĐỒ ÁN TỐT NGHIỆP ĐIỆN TỬ Thiết kế khối điều khiển bộ nhớ SDR-SDRAM

NỘI DUNG ĐỒ ÁN

ĐỒ ÁN TỐT NGHIỆP ĐIỆN TỬ Thiết kế khối điều khiển bộ nhớ SDR-SDRAM

- Tóm tắt Thiết kế khối điều khiển bộ nhớ SDR-SDRAM

Trong nội dung đồ án tốt nghiệp, nhóm chúng tôi sẽ thực hiện “thiết kế khối điều khiển bộ nhớ SDR-SDRAM” thực hiện hai chức năng chính là giám sát và điều khiển.

Chức năng giám sát được thực hiện dựa trên các tín hiệu điều khiển từ khối Initialization để giám sát quá trình khởi động của SDR-SDRAM, cũng như các khoảng thời gian để refresh SDR-SDRAM, đảm bảo không bị mất dữ liệu.

Chức năng điều khiển được thực hiện dựa vào máy trạng thái của khối điều khiển lệnh để tạo ra các lệnh điều khiển việc truy xuất ghi/đọc SDR-SDRAM.

Khối điều khiển có thiết kế thêm phần giao tiếp AHB bus để dễ dàng tích hợp vào các hệ thống SoC, trong đó chip điều khiển chính là chip điều khiển ARM.

Ngoài ra, khối điều khiển SDR-SDRAM còn được kiểm tra, ràng buộc chặt chẽ về định thời, điện áp, diện tích… bằng việc sử dụng các tool chuyên dụng về thiết kế chip như Design Compiler, Prime Time, IC Compiler của hãng Synopsys để tối ưu thiết kế và có thể đưa đến nhà máy để sản xuất thực tế.

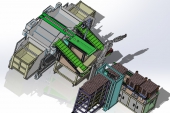

Từ những ý tưởng trên nhóm chúng tôi đã hình thành sơ đồ khối điều khiển SDR-SDRAM như sau :

Hình 1 Sơ đồ khối tổng quát

Nguyên lý hoạt động của khối điều khiển SDR-SDRAM: Khối điều khiển sẽ nhận các tín hiệu đọc/ghi địa chỉ và dữ liệu từ Bus AHB và lưu tạm vào các FIFO trong khối AHB WRAPPER, sau đó khối này sẽ tạo ra các yêu cầu đọc/ghi, thông tin về kích thước burst, kiểu ghi (burst hay single…) để đưa qua khối SDRC CORE CONTROLLER. Khối INITIALIZATION sẽ thực hiện việc khởi động SDR-SDRAM, khối Auto refresh thực hiện làm tươi SDR-SDRAM theo chu kỳ và khối COMMAND CONTROLLER sẽ thực hiện việc tạo ra các lệnh và các tín hiệu điều khiển việc ghi/đọc SDR-SDRAM.

- Nội dung nghiên cứu

Để thực hiện thành công thiết kế “khối điều khiển bộ nhớ SDR-SDRAM” nhóm tôi lần lượt nghiên cứu các nội dung lý thuyết liên quan:

- Nghiên cứu tổng quan về bộ nhớ RAM.

- Nghiên cứu tổng quan về các loại Bus.

- Nghiên cứu tổng quan về chuẩn giao tiếp AHB Bus.

- Nghiên cứu về cấu trúc bên trong và tập lệnh hoạt động của SDR-SDRAM.

- Nghiên cứu về luồng thiết kế ASIC và hoạt động các cổng Logic trong thiết kế.

Những nội dung lý thuyết nêu trên được trình bày lần lượt trong chương 2 và một phần trong chương 3 của đồ án.

- Kết quả nghiên cứu và đánh giá

3.1 Kết quả

Sau thời gian nghiên cứu nội dung lý thuyết và bắt tay vào thiết kế, thực thi, nhóm chúng tôi đã hoàn thành việc xây dựng sơ đồ khối, thiết kế và phân tích các khối chức năng trong thiết kế. Sử dụng các phần mềm như Quartus, ModelSim để kiểm tra và mô phỏng cũng như tối ưu hóa thiết kế; dùng các tool DC, PT, ICC của hãng Synopsys để tổng hợp, ràng buộc, và layout sau đó xuất ra file GDSII để có thể đưa đến nhà máy sản xuất. Các nội dung này chúng tôi lần lượt trình bày trong chương 3 và chương 5 của đồ án.

3.2 Đánh giá

Để đánh giá hoạt động của hệ thống, nhóm tôi viết thêm khối AHB Master model và gắn thêm Model MT48LC64M8A2 (16Meg x 8 x 4 Banks) của hãng Micron thay cho SDRAM để điều khiển. Nội dung chương 4 sẽ trình bày về những kết quả mà hệ thống đạt được và hướng phát triển đề tài.

- Quá trình khởi động SDR-SDRAM:

Hình 2 Quá trình khởi động SDR-SDRAM

- Hoạt động ghi vào Model SDR-SDRAM trong trường hợp Burst Length bằng 8, tại Bank0, Row3:

Hình 3 Hoạt động ghi vào Model SDR-SDRAM

- Hoạt động đọc Model SDR-SDRAM trong trường hợp Burst Length bằng 8, tại Bank0, Row3:

Hình 4 Hoạt động đọc ra Model SDR-SDRAM

- File sau khi chạy layout bằng tool IC Compiler:

Hình 5 Kết quả sau khi chạy layout

Report: design

-physical

Design: sdr_top

Library Name: sdr_top.mw

Cell Name: sdr_top.CEL;1

Target Libraries: saed90nm_typ_ht.db

Link Libraries : *

saed90nm_typ_ht.db

MW Ref Libraries: /root/pro_dn/90EDU/library/saed90nm_dv

Design Statistics:

Number of Module Cells: 2380

Number of Pins: 14727

Number of IO Pins: 117

Number of Nets: 2504

Average Pins Per Net (Signal): 3.72062

Chip Utilization:

Total Std Cell Area: 38451.92

Core Size: width 277.12, height 276.48; area 76618.14

Chip Size: width 325.12, height 324.48; area 105494.94

Std cells utilization: 50.19%

Cell/Core Ratio: 50.19%

Cell/Chip Ratio: 36.45%

Number of Cell Rows: 96

Hình 6 Các thông số cơ bản của lõi IP sau khi layout

Như vậy việc ghi dữ liệu vào và đọc dữ liệu ra SDR-SDRAM đã đúng theo yêu cầu, thiết kế đã đi đến bước cuối cùng là chạy layout.

- Kết luận

Khối điều khiển chip bộ nhớ SDR-SDRAM thực hiện chức năng giám sát và điều khiển hoạt động của SDR-SDRAM. Mặc dù vậy, khối điều khiển cần có những hướng phát triển mới trong tương lai để đáp ứng những nhu cầu ngày càng cao của hệ thống.

MỤC LỤC

LỜI CAM ĐOAN..

PHÂN CÔNG NHIỆM VỤ..

DANH MỤC TỪ VIẾT TẮT..

LỜI MỞ ĐẦU..

CHƯƠNG 1 GIỚI THIỆU VỀ ĐỀ TÀI1

1.1. Giới thiệu chương. 1

1.2. Đặt vấn đề. 1

1.3. Mục tiêu của đề tài1

1.4. Phạm vi của đề tài2

1.5. Phương pháp luận. 2

1.5.1. Mô hình đề xuất3

1.6. Kết luận chương. 4

CHƯƠNG 2 LÝ THUYẾT TỔNG QUAN.. 5

2.1. Giới thiệu chương. 5

2.2. Các khái niệm liên quan đến bộ nhớ. 5

2.2.1. Bộ nhớ RAM... 5

2.2.1.1. Giới thiệu về RAM... 5

2.2.1.2. Đặc trưng. 6

2.2.1.3. Phân loại6

2.2.1.3.1. RAM tĩnh. 6

2.2.1.3.2. RAM động. 7

2.2.1.4. Các loại DRAM... 8

2.2.2. Chuẩn giao tiếp AHB Bus giao tiếp với vi điều khiển ARM... 10

2.2.3.1. Giới thiệu cấu trúc ARM... 10

2.2.3.2. Kiến trúc bus truyền dữ liệu cao cấp của vi điều khiển ARM... 10

2.2.3.3. Bộ nhớ SDR-SDRAM... 11

2.3.1. Hiểu về bộ nhớ SDR-SDRAM... 11

2.3.2. Các lệnh điều khiển SDR-SDRAM... 16

2.3.2.1. Lệnh INHIBIT.. 16

2.3.2.2. Lệnh NOP (NO OPERATION). 16

2.3.2.4. Lệnh ACTIVE.. 16

2.3.2.5. Lệnh PRECHARGE.. 16

2.3.2.6. Lệnh BURST TERMINATE.. 16

2.3.2.7. Lệnh AUTO REFRESH.. 16

2.3.2.8. Lệnh SELF REFRESH.. 17

2.3.2.9. Lệnh READ.. 17

2.3.2.10. Lệnh WRITE.. 17

2.3.3. Khởi động SDR-SDRAM... 17

2.3.4. Định thời các lệnh cho SDR-SDRAM... 19

2.4. Hoạt động của các cổng Logic sử dụng trong thiết kế. 19

2.4.1. Flip-Flop. 19

2.4.2. Cổng NOT (Cổng đảo). 20

2.4.3. Cổng AND (Cổng và). 20

2.4.4. Cổng OR (Cổng hoặc). 20

2.4.5. Cổng XOR.. 21

2.5. Kết luận chương. 21

Tài liệu và link tham khảo:21

CHƯƠNG 3 THIẾT KẾ VÀ PHÂN TÍCH CÁC KHỐI CHỨC NĂNG.. 22

3.1. Giới thiệu chương. 22

3.2. Luồng thiết kế ASIC trong thiết kế vi mạch. 22

3.2.1. Giới thiệu luồng thiết kế ASIC.. 22

3.2.2. Phân tích luồng thiết ASIC.. 22

3.2.2.1. Đặc tả (Specification ). 22

3.2.2.2. Mã hóa RTL (RLT coding). 23

3.2.2.3. Testbench và mô phỏng. 23

3.2.2.4. Tổng hợp. 23

3.2.2.5. Phân tích định thời trước layout (Pre-layout Timing Analysis). 23

3.2.2.6. Sắp xếp và nối dây tự động (APR). 24

3.2.2.7. Back Annotation. 24

3.2.2.8. Phân tích định thời sau layout (Post-layout Timing Analysis). 24

3.2.2.9. Kiểm tra Logic (Logic Verification). 24

3.3. Phân tích chi tiết về các khối trong thiết kế. 25

3.3.1. Sơ đồ tín hiệu giao tiếp của khối SDR-SDRAM CONTROLLER.. 25

3.3.2. Khối AHB WRAPPER.. 27

3.3.3.1. Sơ đồ tín hiệu vào/ra. 27

3.3.3.2. Write address FIFO.. 29

3.3.3.3. Burst control FIFO.. 30

3.3.3.4. Write data FIFO.. 32

3.3.3.5. Read data FIFO.. 33

3.3.3.6. Các tín hiệu đầu ra của AHB slave. 34

3.3.3.7. Các tín hiệu đầu ra của AHB WRAPPER.. 36

3.3.4. Khối COMMAND.. 38

3.3.4.1. Sơ đồ tín hiệu giao tiếp của khối38

3.3.4.2. Khối điều khiển khởi động SDRAM... 40

3.3.4.3. Máy trạng thái điều khiển quá trình đọc/ghi42

3.3.4.4. Các tín hiệu điều khiển chuyển trạng thái46

3.4. Kết luận chương. 53

CHƯƠNG 4: XÁC MINH VÀ TỐI ƯU HÓA THIẾT KẾ.. 54

4.1. Giới thiệu chương. 54

4.2. Thiết kế khối AHB master. 55

4.2.1. Các tín hiệu giao tiếp. 55

4.2.2. Mạch tạo dữ liệu, địa chỉ tự động. 57

4.2.3. Mạch điều khiển pha. 59

4.2.4. Máy trạng thái và các tín hiệu điều khiển khác. 61

4.3. Model MT48LC64M8A2. 63

4.4. Testbench và kết quả. 63

4.4.1. Quá trình khởi động. 63

4.4.2. Kiểm tra quá trình đọc, ghi, refresh…... 64

4.4.2.1. Kiểm tra đọc/ghi không có Auto Precharge. 64

4.4.2.2. Kiểm tra đọc/ghi không có Auto Precharge. 68

4.4.3. Kiểm tra lỗi69

4.4.4. Kiểm tra các trường hợp khác. 70

4.5. Kết luận chương. 72

CHƯƠNG 5 TỔNG HỢP PHÂN TÍCH VÀ THIẾT KẾ VẬT LÝ.. 73

5.1. Giới thiệu chương. 73

5.2. Tổng hợp thiết kế. 73

5.3. Phân tích định thời76

5.4. Thiết kế vật lý. 78

5.5. Kết luận chương. 82

CHƯƠNG 6 KẾT LUẬN VÀ HƯỚNG PHÁT TRIỂN ĐỀ TÀI83

6.1. Giới thiệu chương. 83

6.2. Kết luận. 83

6.3. Hướng phát triển đề tài83

6.4. Kết luận chương. 83

PHÂN CÔNG NHIỆM VỤ

Đỗ Tiến Thành

- Nghiên cứu các đề tài liên quan

- Đề xuất mô hình tổng quan của lõi IP điều khiển bộ nhớ SDRAM

- Tìm hiểu về nội dung lý thuyết tổng quan về chuẩn giao tiếp AMBA AHB Bus.

- Tìm hiểu về hoạt động của SDRAM thông qua Datasheet chip SDR-SDRAM của hãng Micron.

- Thiết kế khối giao tiếp bộ nhớ SDR-SDRAM với bộ xử lí theo chuẩn giao tiếp AHB Bus.

- Vẽ specification

- Viết chương trình dùng ngôn ngữ Verilog HDL

- Viết testbench chạy mô phỏng để kiểm tra và sửa lỗi trong thiết kế.

- Thực hiện việc dùng các tool tổng hợp thiết kế, phân tích định thời và thiết kế vật lý lõi IP.

Cao Thanh Đàm

- Nghiên cứu các đề tài liên quan

- Đề xuất mô hình tổng quan của lõi IP điều khiển bộ nhớ SDRAM

- Tìm hiểu về nội dung lý thuyết tổng quan về tập lệnh của SDRAM

- Tìm hiểu về hoạt động của SDRAM thông qua Datasheet chip SDR-SDRAM của hãng Micron.

- Thiết kế khối thực hiện lệnh điều khiển SDR-SDRAM

- Vẽ specification

- Viết chương trình dùng ngôn ngữ Verilog HDL

- Viết testbench chạy mô phỏng để kiểm tra và sửa lỗi trong thiết kế.

- Thực hiện việc xác minh và tối ưu hóa thiết kế.

- Layout thiết kế

DANH MỤC TỪ VIẾT TẮT

SDR Single Data Rate

RAM Ramdom Access Memory

SRAM Static RAM

DRAM Dynamic RAM

SDRAM Synchronous Dynamic RAM

DDR2 SDRAM Double Data Rate 2 SDRAM

DDR3 SDRAM Double Data Rate III Synchronous Dynamic RAM

SoC System on Chip

AHB Advanced High-performance Bus

FIFO First In First Out

CMOS Complementary metal–oxide–semiconductor

EEPROM Electrically Erasable Programmable Read Only Memory

EPROM Erasable Programmable Read Only Memory

IC Integrated Circuit

PC Personal Computer

ROM Read Only Memory

ASIC Application Specific Integrated Circuit

DC Design Compiler

PT Prime Time

ICC IC Compiler

AMBA Advanced Microcontroller Bus Architecture

IP Intellectual property

SDRC SDRAM Controller

FSM Finite State Machine

MUX Multiplexer

FF Flip-flop

LỜI MỞ ĐẦU

Ngày nay, trong toàn bộ các hệ thống máy tính cũng như trong các chip vi xử lí đều sử dụng RAM làm bộ nhớ chính. RAM là bộ phận quan trọng quyết định đến tốc độ làm việc của hệ thống và làm tăng hiệu suất của hệ thống.

SDR-SDRAM là bộ nhớ phổ biến trong các chip vi điều khiển hay chip SoC, nếu không có phần cứng hỗ trợ điều khiển bộ nhớ này thì người sử dụng phải viết code rất nhiều thông qua các chân điều khiển và việc làm này cũng không đơn giản.

Nếu có phần cứng hỗ trợ, như lõi IP điều khiển SDR-SDRAM tích hợp vào một hệ thống SoC thì người sử dụng chỉ cần cấu hình theo ý muốn sau đó chỉ đọc, ghi dữ liệu và lõi IP sẽ tự động khởi động SDRAM, phát các lệnh cần thiết của SDR-SDRAM để giám sát hoạt động đảm bảo SDR-SDRAM hoạt động bình thường.

Trong nội dung đồ án tốt nghiệp, nhóm chúng tôi sẽ thực hiện việc “thiết kế lõi IP điều khiển bộ nhớ SDR-SDRAM” với các đặc điểm chính như sau:

- Tương thích với bus AMBA AHB giao tiếp với chip vi điều khiển ARM.

- Cấu hình trước các tham số định thời (tCL, tRC, tRCD, tRP, tMRD, tRRD, tRFC, tRAS, tWR) trước khi hoạt động.

- Hỗ trợ hầu hết các loại burst AHB (ngoại trừ WRAP16): SINGLE, INCR, WRAP4, INCR4, WRAP8, INCR8, and INCR16.

- Nhận lệnh Load Mode Register (LMR) để lập trình lại bộ nhớ SDRAM trong thời gian đang vận hành.

- Độ rộng bus địa chỉ (địa chỉ bank, địa chỉ hàng - row và địa chỉ cột – column) và độ rộng bus dữ liệu DQ cấu hình được trước khi tổng hợp.

- Có các FIFO hỗ trợ việc đọc/ghi địa chỉ và dữ liệu

Nhằm mục đích làm rõ các nội dung liên quan đến đề tài như mục tiêu của đề tài, phạm vi đề tài, hướng phát triển, và những phần lý thuyết liên quan đến đề tài, cùng với sơ đồ khối của thiết kế, chương trình của lõi IP, đồ án của nhóm chúng tôi trình bày bao gồm 6 chương như sau:

Chương 1: Giới thiệu về đề tài.

Chương 2: Lý thuyết tổng quan.

Chương 3: Thiết kế và phân tích các khối chức năng.

Chương 4: Xác minh và tối ưu hóa thiết kế.

Chương 5: Tổng hợp phân tích và thiết kế vật lý.

Chương 6: Kết luận và hướng phát triển đề tài.

Xuất phát từ nhu cầu thực tế cần thiết phải xây dựng lõi IP điều khiển bộ nhớ SDRAM có thể cấu hình các thông số trước và điều khiển các hoạt động của SDRAM, nhóm chúng tôi đã tiến hành tìm hiểu các những lý thuyết liên quan tới đề tài cũng như nghiên cứu Datasheet chip SDR-SDRAM 512Mb của hãng Micron, thảo luận và thống nhất phương án thiết kế cuối cùng. Tiếp theo đó, nhóm chúng tôi đã thiết kế sơ đồ khối tổng quát và sơ đồ khối chi tiết của lõi IP, xây dựng máy trạng thái, viết chương trình Verilog HDL mô tả toàn bộ thiết kế. Bước cuối cùng, nhóm chúng tôi kết nối các khối trong bộ lõi IP lại, viết testbench kiểm tra kết quả trên phần mềm Modelsim của hãng Altera và điều khiển SDR-SDRAM thông qua việc sử dụng Model MT48LC64M8A2 (16Meg x 8 x 4 Banks) của hãng Micron, đối chiếu so sánh với yêu cầu đặt ra ban đầu và với các đề tài đã thực hiện trước đó, đánh giá hoạt động của lõi IP dựa trên kết quả thu được. Sau khi kiểm tra đúng chức năng, nhóm chúng tôi sử dụng các tool Design Compiler, Prime Time, IC compiler của hãng Synopsys để kiểm tra, ràng buộc chặt chẽ về timing, sau đó xuất ra file GDSII để có thể gửi đi tới nhà máy để sản xuất ra sản phẩm ứng dụng vào thực tế.

Nhờ sự hướng dẫn tận tình của thầy Võ Tuấn Minh, cũng như sự nỗ lực khắc phục khó khăn phát sinh trong suốt quá trình thực hiện đồ án, nhóm chúng tôi đã hoàn thành mục tiêu “thiết kế lõi IP điều khiển bộ nhớ SDR-SDRAM” thực hiện chức năng giám sát và điều khiển hoạt động của SDR-SDRAM.

CHƯƠNG 1 GIỚI THIỆU VỀ ĐỀ TÀI

1.1. Giới thiệu chương

Lõi IP điều khiển bộ nhớ SDR-SDRAM giúp người sử dụng tích hợp vào các hệ thống SoC, để giám sát và điều khiển hoạt động truy xuất đọc/ghi SDR-SDRAM. Để thiết kế và thực hiện thành công lõi IP cần phải trải qua nhiểu giai đoạn từ việc hình thành ý tưởng, tìm hiểu lý thuyết liên quan đến việc xây dựng sơ đồ khối, viết code verilog, viết testbench kiểm tra chức năng, đến việc tổng hợp, phân tích timing và chạy layout. Phần đầu của chương này sẽ trình bày ý tưởng hình thành nên đề tài. Những ý tưởng này sẽ làm nền tảng để thiết lập mục tiêu mà đề tài cần đạt được. Tiếp theo đó, nội dung chương sẽ lần lượt đề cập đến phạm vi của đề tài và phương pháp nghiên cứu. Cuối cùng là phần kết luận chương.

1.2. Đặt vấn đề

Ngày nay, trong toàn bộ các hệ thống máy tính cũng như trong các chip vi xử lí đều sử dụng RAM làm bộ nhớ chính. RAM là bộ phận quan trọng quyết định đến tốc độ làm việc của hệ thống và làm tăng hiệu suất của hệ thống.

SDR-SDRAM là bộ nhớ phổ biến trong các chip vi điều khiển hay chip SoC, nếu không có phần cứng hỗ trợ điều khiển bộ nhớ này thì người sử dụng phải viết code rất nhiều thông qua các chân điều khiển và việc làm này cũng không đơn giản.

Nếu có phần cứng hỗ trợ, như lõi IP điều khiển SDR-SDRAM tích hợp vào một hệ thống SoC thì người sử dụng chỉ cần cấu hình theo ý muốn sau đó chỉ đọc, ghi dữ liệu và lõi IP sẽ tự động khởi động SDRAM, phát các lệnh cần thiết của SDR-SDRAM để giám sát hoạt động đảm bảo SDR-SDRAM hoạt động bình thường.

1.3. Mục tiêu của đề tài

Từ ý tưởng ban đầu, dựa vào những kiến thức đã được học, nhóm chúng tôi tiến hành tìm hiểu những lý thuyết liên quan và sau đó bắt tay vào thiết kế và thực hiện từng công đoạn.

Mục tiêu của đề tài là thiết kế lõi IP, thực hiện đúng chức năng giám sát và điều khiển bộ nhớ SDR-SDRAM. Bên cạnh đó, thực hiện việc tổng hợp, kiểm tra, phân tích định thời, sắp xếp và nối dây tự động để đưa ra bản layout cuối cùng, có thể đưa đến nhà máy sản xuất ra sản phẩm thực tế. Tối ưu hóa về diện tích, timing cũng như công suất của thiết kế. Lõi IP hoạt động với tần số xung clock hệ thống là 100 Mhz, quá trình tổng hợp dùng thư viện công nghệ 90 nm.

1.4. Phạm vi của đề tài

Trong nội dung đồ án tốt nghiệp, nhóm chúng tôi sẽ lần lượt thực hiện việc thiết kế lõi IP điều khiển bộ nhớ SDR-SDRAM, từ công đoạn phân tích, đưa ra ý tưởng, đến việc xây dựng sơ đồ khối, viết code, viết testbench, tổng hợp và phân tích trên các tool DC, PT và cuối cùng là chạy layout bằng tool ICC.

1.5. Phương pháp luận

Quá trình thực hiện đồ án tốt nghiệp của nhóm chúng tôi trải qua nhiều giai đoạn khác nhau, ứng với mỗi giai đoạn cần đưa ra một phương pháp nghiên cứu phù hợp để công việc được giải quyết nhanh và hiệu quả.

- Trong giai đoạn đầu của đồ án, nhóm tìm hiểu những đề tài có liên quan, đưa ra những ý tưởng ban đầu.

- Trong giai đoạn tiếp theo, nhóm tiến hành tìm hiểu những nội dung lý thuyết liên quan. Việc tìm hiểu các đề tài liên quan đến nội dung đồ án là khá quan trọng vì nó giúp chúng tôi bước đầu xây dựng được sơ đồ khối tổng quát và lựa chọn được giải pháp thiết kế phù hợp với đề tài.

- Sau khi xây dựng thành công sơ đồ khối tổng quát, chúng tôi lần lượt đi vào thiết kế từng khối trong sơ đồ.

- Để đánh giá hoạt động của lõi IP, nhóm chúng tôi nhóm chúng tôi kết nối các khối trong bộ điều khiển lại, viết testbench kiểm tra kết quả trên phần mềm Modelsim của hãng Altera và điều khiển SDR-SDRAM thông qua việc sử dụng Model MT48LC64M8A2 (16Meg x 8 x 4 Banks) của hãng Micron, đối chiếu so sánh với yêu cầu đặt ra ban đầu, đánh giá hoạt động của lõi IP dựa trên kết quả thu được. Sau khi kiểm tra đúng chức năng, nhóm chúng tôi sử dụng các tool Design Compiler, Prime Time, IC compiler của hãng Synopsys để kiểm tra, ràng buộc chặt chẽ về timing, sau đó xuất ra file GDSII để có thể gửi đi tới nhà máy để sản xuất ra sản phẩm ứng dụng vào thực tế.

1.5.1. Mô hình đề xuất

Hình 1.1 Mô hình đề xuất

Cấu trúc cơ bản của lõi IP điều khiển SDR-SDRAM gồm 2 khối chức năng chính:

- AHB WRAPPER: Khối xử lý các giao tiếp với AHB Bus. Khối này chứa 4 FIFO phục vụ lưu địa chỉ và lưu dữ liệu cho quá trình ghi/đọc dữ liệu từ SDR-SDRAM:

o Write address FIFO: có độ sâu là 16 tầng (stage), để lưu địa chỉ ghi vào SDR-SDRAM.

o Write burt control FIFO: có độ sâu 16 tầng, để lưu thông tin về burst gồm: burst type (3 bit), first beat (1 bit), last beat (1 bit).

o Write data FIFO: có độ sâu 16 tầng, để lưu dữ liệu ghi vào SDR-SDRAM.

o Read data FIFO: có độ sâu 16 tầng, để lưu dữ liệu đọc ra từ SDR-SDRAM khi mà AHB Master đang bận.

- SDRC CORE CONTROLLER: Khối điều khiển giao tiếp trực tiếp với SDR-SDRAM. Khối này nhận các tín hiệu từ khối AHB WRAPPER, bên trong khối này bao gồm 3 khối nhỏ:

o INITIALZATION: thực hiện việc khởi động SDR-SDRAM.

o AUTO REFRESH: thực hiện việc làm tươi SDR-SDRAM theo chu kỳ.

o COMMAND CONTROLLER: Máy trạng thái tạo ra các lệnh điều khiển truy xuất đọc/ghi SDR-SDRAM.

1.6. Kết luận chương

Từ ý tưởng thiết kế ban đầu đến khi hoàn thành thiết kế là một quá trình dài bao gồm nhiều giai đoạn khác nhau, trong mỗi giai đoạn sẽ yêu cầu những phương pháp nghiên cứu riêng. Nội dung chương này mang tính định hướng, làm nền tảng để các chương sau đi sâu vào nghiên cứu các vấn đề cụ thể liên quan đến đề tài.

CHƯƠNG 2 LÝ THUYẾT TỔNG QUAN

2.1. Giới thiệu chương

Từ sơ đồ khối tổng quan được đề xuất, nhóm chúng tôi lần lượt tìm hiểu những nội dung lý thuyết liên quan.

- Tìm hiểu về bộ nhớ RAM, cách phân loại và phân biệt giữa các loại RAM.

- Tìm hiểu chuẩn giao tiếp AHB Bus giao tiếp với chip vi điều khiển ARM.

- Tìm hiểu về cấu trúc bên trong của SDR-SDRAM và tập lệnh hoạt động của SDR-SDRAM dựa vào Datasheet của hãng Micron.

- Tìm hiểu hoạt động các cồng logic sử dụng trong thiết kế.

Việc tìm hiểu những lý thuyết này rất quan trọng vì phải hiểu rõ cấu trúc cũng như cách thức hoạt động của bộ nhớ SDR-SDRAM, từ đó mới có thể thiết kế bộ điều khiển cho phù hợp với hoạt động của SDR-SDRAM.

2.2. Các khái niệm liên quan đến bộ nhớ

2.2.1. Bộ nhớ RAM

2.2.1.1. Giới thiệu về RAM

RAM (viết tắt từ Random Access Memory) là một loại bộ nhớ chính của máy tính. RAM được gọi là bộ nhớ truy xuất ngẫu nhiên vì nó có đặc tính: thời gian thực hiện thao tác đọc hoặc ghi đối với mỗi ô nhớ là như nhau, cho dù đang ở bất kỳ vị trí nào trong bộ nhớ. Mỗi ô nhớ của RAM đều có một địa chỉ. Thông thường, mỗi ô nhớ là một byte (8 bit); tuy nhiên hệ thống lại có thể đọc ra hay ghi vào nhiều byte (2, 4, 8 byte).

Bởi vì các chip RAM có thể đọc hay ghi dữ liệu nên thuật ngữ RAM cũng được hiểu như là một bộ nhớ đọc-ghi (read/write memory), trái ngược với bộ nhớ chỉ đọc ROM (read-only memory).

RAM thông thường được sử dụng cho bộ nhớ chính (main memory) trong máy tính để lưu trữ các thông tin thay đổi, và các thông tin được sử dụng hiện hành. Cũng có những thiết bị sử dụng một vài loại RAM như là một thiết bị lưu trữ thứ cấp (secondary storage). Thông tin lưu trên RAM chỉ là tạm thời, chúng sẽ mất đi khi mất nguồn điện cung cấp.

Hình 2.1 Một số loại RAM: 1-DIP, 2-SIPP, 3- SIMM 30 chân, 4-SIMM 72 chân,

5-DIMM (168 chân),6-DDR DIMM (184-chân) [1]

2.2.1.2. Đặc trưng

Bộ nhớ RAM có 4 đặc trưng sau:

- Dung lượng bộ nhớ: tổng số byte của bộ nhớ (nếu tính theo byte) hoặc là tổng số bit trong bộ nhớ nếu tính theo bit.

- Tổ chức bộ nhớ: số ô nhớ và số bit cho mỗi ô nhớ

- Thời gian thâm nhập: thời gian từ lúc đưa ra địa chỉ của ô nhớ đến lúc đọc được nội dung của ô nhớ đó.

- Chu kỳ bộ nhớ: thời gian giữa hai lần liên tiếp thâm nhập bộ nhớ.

2.2.1.3. Phân loại

Tùy theo công nghệ chế tạo, người ta phân biệt thành 2 loại: SRAM (Static RAM): RAM tĩnh và DRAM (Dynamic RAM): RAM động

2.2.1.3.1. RAM tĩnh

RAM tĩnh là một dạng bộ nhớ bán dẫn sử sụng mạch chốt 2 trạng thái bền (bistable latching circuit) để lưu trữ mỗi bit.

Hình 2.2 6 transistor trong một cel ô nhớ của RAM tĩnh [1]

SRAM là bộ nhớ nhanh, việc đọc không làm hủy nội dung của ô nhớ và thời gian thâm nhập bằng chu kỳ của bộ nhớ. Các đặc tính trên khiến SRAM đắt hơn nhiều so với DRAM và nó chủ yếu được dùng làm bộ nhớ đệm (cache) trong CPU.

2.2.1.3.2. RAM động

Hình 2.3 Transistor và tụ điện trong một cel ô nhớ của RAM động [1]

RAM động dùng kỹ thuật MOS. Mỗi bit nhớ gồm một transistor và một tụ điện. Việc ghi nhớ dữ liệu dựa vào việc duy trì điện tích nạp vào tụ điện và như vậy việc đọc một bit nhớ làm nội dung bit này bị hủy. Do vậy sau mỗi lần đọc một ô nhớ, bộ phận điều khiển bộ nhớ phải viết lại nội dung ô nhớ đó.

Việc lưu giữ thông tin trong bit nhớ chỉ là tạm thời vì tụ điện sẽ phóng hết điện tích đã nạp và như vậy phải làm tươi bộ nhớ sau khoảng thời gian 2μs. Việc làm tươi được thực hiện với tất cả các ô nhớ trong bộ nhớ. Công việc này được thực hiện tự động bởi một vi mạch bộ nhớ.

2.2.1.4. Các loại DRAM

SDRAM (Viết tắt từ Synchronous Dynamic RAM) được gọi là DRAM đồng bộ. SDRAM gồm 4 phân loại: SDR, DDR, DDR2 và DDR3.

o SDR SDRAM (Single Data Rate SDRAM), thường được gọi tắt là "SDR". Có 168 chân. Được dùng trong các máy vi tính cũ, bus speed chạy cùng vận tốc với clock speed của memory chip.

o DDR SDRAM (Double Data Rate SDRAM), thường được gọi tắt là "DDR". Có 184 chân. DDR SDRAM là cải tiến của bộ nhớ SDR với tốc độ truyền tải gấp đôi SDR nhờ vào việc truyền tải hai lần trong một chu kỳ bộ nhớ. Đã được thay thế bởi DDR2.

Hình 2.4 Hoạt động của SDR và DDR SDRAM [1]

o DDR2 SDRAM (Double Data Rate 2 SDRAM), Thường được gọi tắt là "DDR2". Là thế hệ thứ hai của DDR với 240 chân, lợi thế lớn nhất của nó so với DDR là có bus speed cao gấp đôi clock speed.

Hình 2.5 So sánh tần số hoạt động của SDR, DDR và DDR2 SDRAM [1]

o DDR3 SDRAM (Double Data Rate III Synchronous Dynamic RAM): có tốc độ bus 800/1066/1333/1600 Mhz, số bit dữ liệu là 64, điện thế là 1.5v, tổng số pin là 240.

2.2.2. Chuẩn giao tiếp AHB Bus giao tiếp với vi điều khiển ARM

2.2.3.1. Giới thiệu cấu trúc ARM

Cấu trúc ARM (viết tắt từ Advanced RISC Machine) là một loại cấu trúc vi xử lý32-bit kiểu RISC được sử dụng rộng rãi trong các thiết kế nhúng.

2.2.3.2. Kiến trúc bus truyền dữ liệu cao cấp của vi điều khiển ARM

ARM giao tiếp với các khối ngoại vi bởi hệ thống bus truyền dữ liệu cao cấp AMBA (Advanced Microcontroller Bus Architecture). Đặc điểm của AMBA là chuẩn truyền thông trên chip dành cho thiết kế các vi điều khiển 16 và 32 bit với hiệu suất cao, các bộ xử lý tín hiệu và các thiết bị ngoại vi phức tạp. Đặc tính kỹ thuật AMBA: Bus băng thông rộng, tốc độ cao, Bus ngoại vi có công suất thấp, cấu trúc đơn giản.

Kiến trúc AMBA điển hình:

Hình 2.6 Vi điều khiển dựa trên kiến trúc AMBA điển hình [2]

Trong đó:

o Bus hệ thống hiệu suất cao (AHB - Advanced High Performace Bus): Bus này đảm bảo tốc độ dữ liệu giữa hệ thống với các giao tiếp bus bên ngoài. Bộ xử lý trung tâm (CPU), các bus truyền chính khác (như bộ điều khiển truy cập bộ nhớ trực tiếp DMA), bộ nhớ trong cũng được kết nối với bus truyền tốc độ cao này. AHB được kết nối với APB bởi cầu nối.

o Bus truyền dữ liệu ngoại vi tối ưu (APB - Advanced Peripheral Bus): bus truyền ngoại vi này có công suất thấp, tốc độ thấp và đơn giản.

2.2.3.3. Bộ nhớ SDR-SDRAM

2.3.1. Hiểu về bộ nhớ SDR-SDRAM

SDR-SDRAM (viết tắt của từ Single Data Rate Synchronous Dynamic Random Access Memory): bộ nhớ động truy cập ngẫu nhiên đồng bộ đơn tốc độ.

Hình 2.7 Các chip SDR-SDRAM trên 1 thanh SDRAM của PC [5]

Khi xem Datasheet hay 1 mô tả về SDR-SDRAM, dung lượng bộ nhớ thường được biểu diễn kiểu: 32 Meg x 4 x 4 banks theo thứ tự từ trái qua phải là: số lượng ô nhớ trong 1 bank, số bit trong 1 ô nhớ, số bank. Như ví dụ trên thì SDR-SDRAM này có 4 bank, mỗi bank có 32Mega ô nhớ, mỗi ô nhớ có 4 bit. Vậy dung lượng của bộ nhớ này là 32M x 4bit x 4bank = 512 Mbit.

Vị trí của 1 ô nhớ của SDR-SDRAM được xác định bởi 3 địa chỉ là: địa chỉ bank (bank address), địa chỉ hàng (row address), địa chỉ cột (column address), và được biểu diễn như sau:

Hình 2.8 Bộ nhớ có dung lượng 32 Meg x 4 x 4 banks(512 Mbit) [5]

Cấu trúc bên trong của 1 chip SDR-SDRAM: ngoài các mảng ô nhớ thì còn có các mạch số thực hiện giải mã lệnh, giải mã địa chỉ và thực thi các chức năng khác.

Hình 2.9 Cấu trúc bên trong của 1 chip SDR-SDRAM [5]

Các tín hiệu giao tiếp của chip SDR-SDRAM:

|

Tín hiệu |

Chiều |

Mô tả |

|

CLK |

IN |

Clock hệ thống, hoạt động theo cạnh lên. |

|

CKE |

IN |

Clock Enable: cho phép clock hoạt động |

|

CS# |

IN |

Chip Select: chọn chip, tích cực mức thấp. Khi ở mức cao, bộ giải mã sẽ bỏ qua các tín hiệu điều khiển khác. |

|

DQM |

IN |

Data Mask: khi ở mức cao, tín hiệu này cấm dữ liệu đọc/ghi. |

|

RAS#, CAS#, WE# |

IN |

Tổ hợp 3 tín hiệu này dùng để định nghĩa lệnh điều khiển SDRAM. |

|

BA |

IN |

Bank Address: dùng để chọn bank. |

|

A0 – A12 |

IN |

Bus địa chỉ: Đối với lệnh ACTIVE, nó là địa chỉ hàng, còn đối với lệnh READ/WRITE thì nó là địa chỉ cột. Riêng A10 dùng để chọn chức năng Auto Recharge. |

|

DQ |

IN/OUT |

Bus dữ liệu, độ rộng là 4/8/16 bit tùy vào loại SDRAM. |

Bảng 2.1 Các tín hiệu giao tiếp của chip SDR-SDRAM

Thanh ghi cấu hình hoạt động của SDR-SDRAM (MODE REGISTER): trước khi truy xuất (đọc/ghi) SDRAM thì thanh ghi này phải được cấu hình các giá trị phù hợp thông qua lệnh LOAD (SET) MODE REGISTER. Thanh ghi này có cấu trúc như hình 2.18. Trong đó:

o WB (Write Burst Mode): 1 bit chọn kiểu burst hay single. Nếu chọn kiểu burst thì phải quan tâm đến các bit BT và Burst Length.

o BT (Burst Type): 1 bit chọn chế độ burst là tuần tự (sequential) hay xen kẽ (interleaved).

Hình 2.10 Thanh ghi cấu hình hoạt động của SDR-SDRAM [5]

o Burst Length: 3 bit chọn độ dài burst tối đa cho một lần truy xuất (đọc/ghi) SDRAM. Tùy theo kiểu burst đã chọn mà thứ tự địa chỉ truy xuất sẽ khác nhau như bảng sau 2.2.

o CAS Latency (CL): Độ trễ của dữ liệu đọc tính từ khi SDRAM nhận lệnh đọc đến khi dữ liệu được trả trên bus dữ liệu DQ. Chỉ có 2 giá trị được phép sử dụng là 2 hoặc 3, tương ứng sau 2 hoặc 3 xung clock CLK SDRAM sẽ trả dữ liệu như hình 2.11.

o Op mode: Hai bit chỉ chế độ xử lí của SDRAM.

Bảng 2.2 Thứ tự truy xuất địa chỉ của SDR-SDRAM [5]

..........................

Hình 5.5 Kết quả báo cáo về timing

Kết quả cho thấy tất cả các nhóm hclk, combo, inputs, outputs đều có slack là số dương, chứng tỏ rằng thiết kế không bị vi phạm về timing.

- Báo cáo về diện tích:

Hình 5.6 Báo cáo về diện tích

5.1. Phân tích định thời

Sau khi đã tổng hợp DC xong, dùng tool Prime Time (PT) để phân tích thời gian, độ tin cậy của tool PT cao nhất, dùng để phân tích trước và sau khi chạy layout.

Đầu vào / ra của phân tích PT:

Hình 5.7 Đầu vào / ra của phân tích PT [7]

Đầu vào của PT: gồm các file gate netlist từ đầu ra của DC, file thư viện công nghệ, file định dạng delay chuẩn (SDF), file ràng buộc timing, file phân tích nhiễu kí sinh. Đầu ra của PT: các file báo cáo về timing, file ràng buộc timing, phân tích nhiễu kí sinh, file delay chuẩn (SDF), các file đưa qua tool ICC để chạy layout.

Luồng phân tích định thời bằng tool PT:

Hình 5.8 Luồng phân tích định thời PT [7]

Sau khi tổng hợp DC, các file gate netlist và file contraints sẽ được đưa vào Pt để phân tích định thời. Sau khi chạy layout xong, các file thiết kế cũng được đưa vào PT để phân tích; cùng với các file trong thư viện công nghệ, timing models… để đưa ra báo cáo ràng buộc chặt chẽ nhất về timing, đảm bảo không bị vi phạm.

Kết quả sau khi phân tích thiết kế:

- Báo cáo về phân tích độ bao phủ thiết kế:

Hình 5.9 Báo cáo độ bao phủ thiết kế

Như kết quả trên thì thiết kế không bị vi phạm, độ bao phủ là 94% khá cao, đạt yêu cầu (>90%).

- Báo cáo về timing:

Hình 5.10 Báo cáo timing sử dụng PT

Kết quả báo cáo slack có giá trị dương nên thiết kế không bị vi phạm về timing.

5.2. Thiết kế vật lý

Sau khi phân tích định thời, dùng tool IC Compiler (ICC) để sắp xếp và nối dây tự động. Đầu vào / ra của tool ICC:

Hình 5.11 Đầu vào / ra của tool ICC [7]

Đầu vào của ICC: gồm các file netlist đầu ra của PT, file thư viện cell, thư viện công nghệ. Đầu ra của ICC: file verilog, file định dạng nhiễu kí sinh, file GDSII để đưa đến nhà máy sản xuất.

Luồng thiết kế sử dụng tool ICC:

Hình 5.12 Luồng thiết kế của tool ICC [7]

- Data preparation: chuẩn bị thư viện thiết kế, đưa netlist, thư viện công nghệ vào.

- Floorplanning: thiết lập kích thước của thiết kế, sắp xếp vị trí các khối.

- Power planning: tạo các đường nối nguồn và nối với mass.

- Placement: sắp xếp tự động các khối, cell sao cho tối ưu về diện tích, công suất.

- Clock Tree Synthesis: tổng hợp cây clock, cân bằng các đường clock trong thiết kế để tránh vi phạm về timing.

- Routing: nối dây tự động giữa các đường, đảm bảo không vi phạm về timing.

- Finishing: hoàn thành bản layout.

- Results: kết quả là xuất ra các file định dạng để kiểm tra sau layout và file GDSII để đưa đến nhà máy sản xuất.

Kết quả chạy layout thiết kế sử dụng tool ICC:

Hình 5.13 Kết quả chạy layout bằng tool ICC

Report : design

-physical

Design : sdr_top

Library Name: sdr_top.mw

Cell Name: sdr_top.CEL;1

Target Libraries : saed90nm_typ_ht.db

Link Libraries : *

saed90nm_typ_ht.db

MW Ref Libraries : /root/pro_dn/90EDU/library/saed90nm_dv

Design Statistics:

Number of Module Cells: 2380

Number of Pins: 14727

Number of IO Pins: 117

Number of Nets: 2504

Average Pins Per Net (Signal): 3.72062

Chip Utilization:

Total Std Cell Area: 38451.92

Core Size: width 277.12, height 276.48; area 76618.14

Chip Size: width 325.12, height 324.48; area 105494.94

Std cells utilization: 50.19%

Cell/Core Ratio: 50.19%

Cell/Chip Ratio: 36.45%

Number of Cell Rows: 96

Hình 5.14 Các thông số cơ bản của lõi IP sau khi layout

Internal Switching Leakage Total

Power Group Power Power Power Power ( %) Attrs

--------------------------------------------------------------------------------

clock_network 1.700e-05 0.0000 0.0000 1.700e-05 ( 2.54%) i

register -6.794e-07

4.309e-06 3.332e-04 3.368e-04 (50.33%)

combinational 1.473e-05 6.373e-06 2.902e-04 3.113e-04 (46.52%)

sequential -1.752e-07

1.993e-10 4.224e-06 4.049e-06 (0.61%)

memory 0.0000 0.0000 0.0000 0.0000 (0.00%)

io_pad 0.0000 0.0000 0.0000 0.0000 (0.00%)

black_box 0.0000 0.0000 0.0000 0.0000 (0.00%)

Net Switching Power = 1.068e-05 (1.60%)

Cell Internal Power = 3.088e-05 (4.61%)

Cell Leakage Power = 6.277e-04 (93.79%)

---------

Total Power = 6.692e-04 (100.00%)

Hình 5.15 Các thông số về công suất

5.3. Kết luận chương

Thiết kế đã được kiểm tra, phân tích và ràng buộc chặt chẽ về timing và diện tích. Các kết quả báo cáo là cơ sở để kiểm chứng tính đúng đắn và độ tin cậy của thiết kế, đảm bảo thiết kế không bị vi phạm về timing, tối ưu hóa về diện tích cũng như công suất.

Chi tiết về kết quả đạt được:

- Sử dụng công nghệ 90nm

- Tần số hoạt động: 125Mhz (T = 8ns), slack: 0.058ns

- Diện tích core: 76618.14 µm2 (rộng: 277.12 µm , dài 276.48 µm)

- Diện tích chip: 105494.94 µm2 (rộng: 325.12µm , dài 324.48µm)

- Công suất chip: 6.692e-04 W

- Điện áp hoạt động: 1.32V

- Sử dụng 6 lớp metal: từ metal 1 đến metal 6

Tài liệu tham khảo:

[7] Victor Grimblatt R&D Group Director, Digital IC Design, 2012

CHƯƠNG 6 KẾT LUẬN VÀ HƯỚNG PHÁT TRIỂN ĐỀ TÀI

6.1. Giới thiệu chương

Nội dung chương này sẽ trình bày về kết quả đạt được sau khi chạy testbench mô phỏng để kiểm tra chức năng của khối thiết kế. Đối chiếu kết quả so với mục tiêu ban đầu để kết luận và đưa ra hướng phát triển của đề tài trong tương lai.

6.2. Kết luận

Lõi IP điều khiển bộ nhớ SDR-SDRAM thực hiện được chức năng giám sát và điều khiển hoạt động của SDR-SDRAM.

Thiết kế đã đáp ứng được mục tiêu ban đầu đặt ra là điều khiển được việc truy xuất đọc/ghi SDR-SDRAM và đáp ứng được tần số hoạt động là 100 Mhz, thực hiện việc tổng hợp với thư viện công nghệ 90 nm, phân tích, kiểm tra timing, tối ưu thiết kế và chạy ra bản layout để có thể đưa đến nhà máy sản xuất.

Mặc dù vậy, lõi IP cần có những hướng phát triển mới trong tương lai để đáp ứng những nhu cầu ngày càng cao của hệ thống.

6.3. Hướng phát triển đề tài

Tuy thiết kế đã đáp ứng đầy đủ những yêu cầu đặt ra ban đầu nhưng vì đây là một lĩnh vực còn khá mới mẻ và đang được tiếp tục phát triển, nên thiết kế cần có những hướng phát triển mới trong tương lai như sau:

- Tích hợp thêm các chuẩn giao tiếp với khối điểu khiển như: Uart, I2C…

- Tích hợp lõi IP điều khiển vào 1 hệ thống SoC cụ thể.

- Thiết kế lõi IP điều khiển các loại bộ nhớ hiện đại và sử dụng rộng rãi như: DDR-SDRAM, DDR2-SDRAM, DDR3-SDRAM…

6.4. Kết luận chương

Lõi IP điều khiển bộ nhớ “SDR-SDRAM” đã đáp ứng được đầy đủ các yêu cầu kỹ thuật đặt ra. Lõi IP đã thực hiện đúng chức năng truy xuất đọc/ghi bộ nhớ SDR-SDRAM, cũng như giám sát các hoạt động của SDR-SDRAM, khả năng ứng dụng rộng rãi vào thực tế.